I/O-8 EIGHT PORT SERIAL COMMUNICATIONS BOARD **OPERATIONS MANUAL**

SD #7140172 REVISION D NOVEMBER 21, 1983

.

. . .

)

### **EMI NOTICE**

This equipment has been designed and constructed to professional standards. However, the equipment must be utilized correctly by the user to obtain proper performance and to comply with applicable industry and governmental regulations.

Since the equipment is supplied as an unconfigured component and cannot be tested for electro-magnetic interference (EMI) in all possible configurations, the equipment is not subject to standards imposed by Subpart J of Part 15 of FCC Rules and Regulations.

Final system configuration will require compliance with applicable FCC regulations. SDSystems recommends the installation of shielded data cables for all external cabling. Electro-magnetic interference (EMI) levels are dependent upon final system hardware configuration and application.

Contact SDSystems Customer Service if additional configuration information is required.

### **TERMINATION NOTE**

SDSystems recommends the use of active termination circuitry on the S-100 bus to avoid system problems.

## TABLE OF CONTENTS

|   | Subsection<br>Number | Title                                          | Page<br>No. |

|---|----------------------|------------------------------------------------|-------------|

| ) |                      | SECTION I<br>INTRODUCTION                      |             |

|   | 1.0<br>1.1           | GENERAL<br>FEATURES                            | 1-1<br>1-1  |

|   |                      | SECTION II<br>FUNCTIONAL DESCRIPTION           |             |

|   | 2.0                  | GENERAL                                        | 2-1         |

|   | 2.1                  | SERIAL INPUT/OUTPUT                            | 2-1         |

|   | 2.1.1                | SERIAL COMMUNICATIONS                          |             |

|   |                      | CONTROLLER (SCC/ASCC)                          | 2-1         |

|   | 2.1.2                | SERIAL PORT INTERFACE                          | 2-1         |

|   | 2.1.3                | SCC INTERRUPTS                                 | 2-3         |

|   | 2.2                  | REAL TIME CLOCK (RTC)                          | 2-3         |

|   | 2.2.1                | RTC COUNTERS AND RAM                           | 2-3         |

|   | 2.2.2<br>2.2.3       | RTC BATTERY BACKUP                             | 2-4<br>2-4  |

| ) | 2.2.3<br>2.3         | RTC INTERRUPTS<br>BOARD SELECT AND PORT DECODE | 2-4         |

| - | 2.0                  | LOGIC                                          | 2-4         |

|   | 2.4                  | SCC SELECT REGISTER                            | 2-4<br>2-5  |

|   | 2.4                  | RTC ADDRESS SELECT/STATUS                      | 2-0         |

|   | 2.0                  | REGISTER                                       | 2-5         |

|   | 2.6                  | EIGHT BIT SWITCH PORT                          | 2-5         |

|   | 2.7                  | WAIT STATE GENERATOR                           | 2-6         |

|   |                      |                                                |             |

|   |                      | SECTION III                                    |             |

|   |                      | THEORY OF OPERATIONS                           |             |

|   | 3.0                  | GENERAL                                        | 3-1         |

|   | 3.1                  | SERIAL COMMUNICATIONS                          | 3-1         |

|   | 3.1.1                | DCE AND DTE                                    | 3-1         |

|   | 3.1.2                | SYNCHRONOUS AND ASYNCHRONOUS                   |             |

|   |                      | COMMUNICATIONS FORMATS                         | 3-1         |

| ) |                      | SECTION IV                                     |             |

|   |                      | OPERATIONS                                     |             |

|   | 4.0                  | GENERAL                                        | 4-1         |

|   | 4.1                  | BOARD ADDRESSING OPTIONS                       | 4-1         |

|   |                      |                                                |             |

|   |                      | i                                              |             |

# TABLE OF CONTENTS (Continued)

| Subsection<br>Number | Title                                | Page<br>No. |          |

|----------------------|--------------------------------------|-------------|----------|

|                      | SECTION IVContinued                  |             | (        |

|                      | <b>OPERATIONS</b> Continued          |             | <b>\</b> |

| 4.2                  | SERIAL INTERFACE OPTIONS             | 4-3         |          |

| 4.2.1                | TERMINAL OR MODEM CONFIGURATION      |             |          |

|                      | (DCE OR DTE)                         | 4-3         |          |

| 4.2.2                | ASYNCHRONOUS COMMUNICATIONS          | 4-4         |          |

| 4.2.2.1              | FULL INTERFACE CHANNELS (1, 3, 5, 7) | 4-4         |          |

| 4.2.2.2              | PARTIAL INTERFACE CHANNELS           |             |          |

|                      | (2, 4, 6, 8)                         | 4-9         |          |

| 4.2.2.3              | PRINTERS                             | 4-9         |          |

| 4.2.3                | SYNCHRONOUS COMMUNICATIONS           | 4-9         |          |

| 4.3                  | MISCELLANEOUS OPTIONS                | 4-13        |          |

| 4.3.1                | INTERRUPT OPTIONS                    | 4-13        |          |

| 4.3.2                | <b>RESET/SLAVE CLR OPTION</b>        | 4-13        |          |

| 4.3.3                | SCC WAIT LINE OPTION                 | 4-14        |          |

| 4.4                  | PORT ADDRESS MAP                     | 4-14        | (        |

| 4.5                  | SCC PROGRAMMING                      | 4-15        |          |

| 4.5.1                | ASYNCHRONOUS SCC INITIALIZATION      | 4-16        |          |

| 4.5.2                | ASYNCHRONOUS PROGRAMMING             |             |          |

|                      | EXAMPLE                              | 4-17        |          |

| 4.6                  | REAL TIME CLOCK PROGRAMMING          | 4-19        |          |

| 4.6.1                | REAL TIME COUNTER                    | 4-20        |          |

| 4.6.2                | RAM                                  | 4-21        |          |

| 4.6.3                | INTERRUPTS                           | 4-21        |          |

| 4.6.4                | COUNTER AND RAM RESETS               | 4-22        |          |

| 4.6.5                | RTC PROGRAMMING EXAMPLE              | 4-23        |          |

|                      | SECTION V                            |             |          |

|                      | ENVIRONMENTAL CONSIDERATIONS         |             |          |

| 5.0                  | GENERAL                              | 5-1         |          |

| 5-1                  | ELECTRICAL REQUIREMENTS AND          |             | /        |

|                      | SPECIFICATIONS                       | 5-1         | (        |

| 5.1.1                | +5 VOLT REGULATION                   | 5-1         | N.       |

| 5.1.2                | +12 VOLT REGULATION                  | 5-1         |          |

| 5.1.3                | CURRENT CONSUMPTION (ESTIMATED)      | 5-1         |          |

# TABLE OF CONTENTS (Continued)

|   | Subsection<br>Number  | Title                                                                  | Page<br>No.       |

|---|-----------------------|------------------------------------------------------------------------|-------------------|

| ) |                       | SECTION VContinued<br>ENVIRONMENTAL<br>CONSIDERATIONSContinued         |                   |

|   | 5.1.4<br>5.2<br>5.2.1 | POWER CONSUMPTION (ESTIMATED)<br>PHYSICAL SPECIFICATIONS<br>DIMENSIONS | 5-1<br>5-1<br>5-1 |

|   | APPENDIC              | CES                                                                    |                   |

|   | Α                     | SELECTED IEEE-696 SPECIFICATION SHEETS                                 | <b>A</b> -1       |

|   | В                     | BASE CONVERSIONS                                                       | B-1               |

|   | С<br>С                | STANDARD ASCII CODES                                                   | C-1               |

|   | D                     | DISCLAIMER                                                             | D-1               |

|   | Ē                     | LIMITED WARRANTY                                                       | E-1               |

|   | F                     | SAMPLE DRIVER                                                          | F-1               |

| ) | G                     | SCC REGISTERS                                                          | G-1               |

|   | Н                     | PARTS LIST FOR I/O-8                                                   | H-1               |

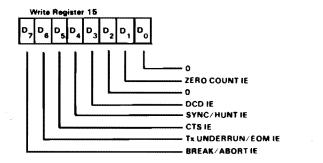

|   | Ι                     | PARTS PLACEMENT DIAGRAM                                                | I-1               |

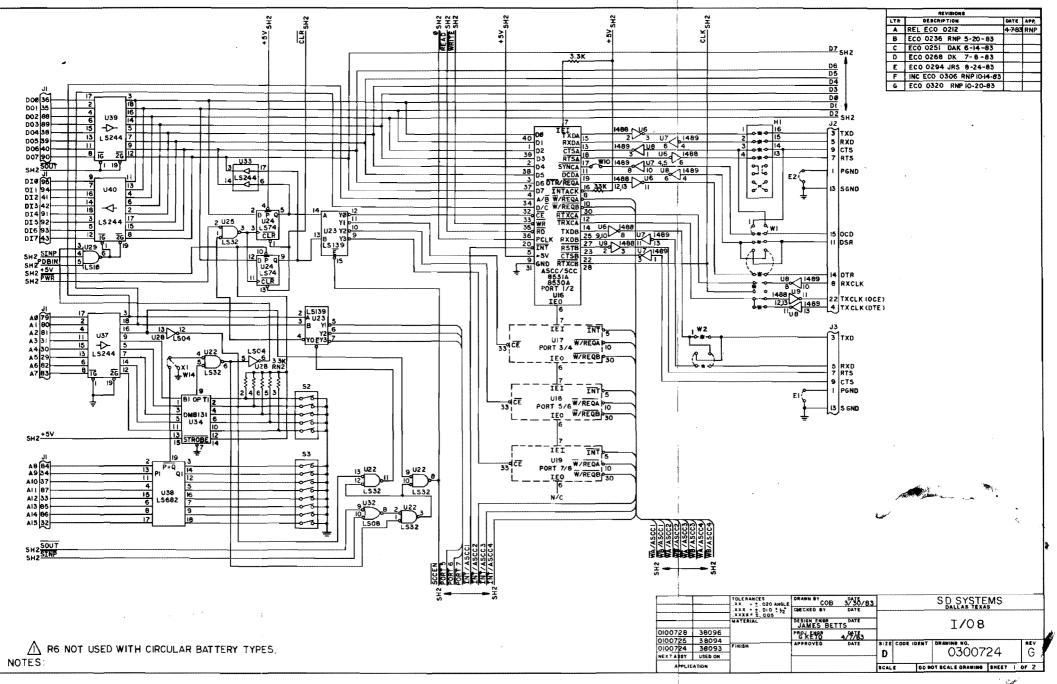

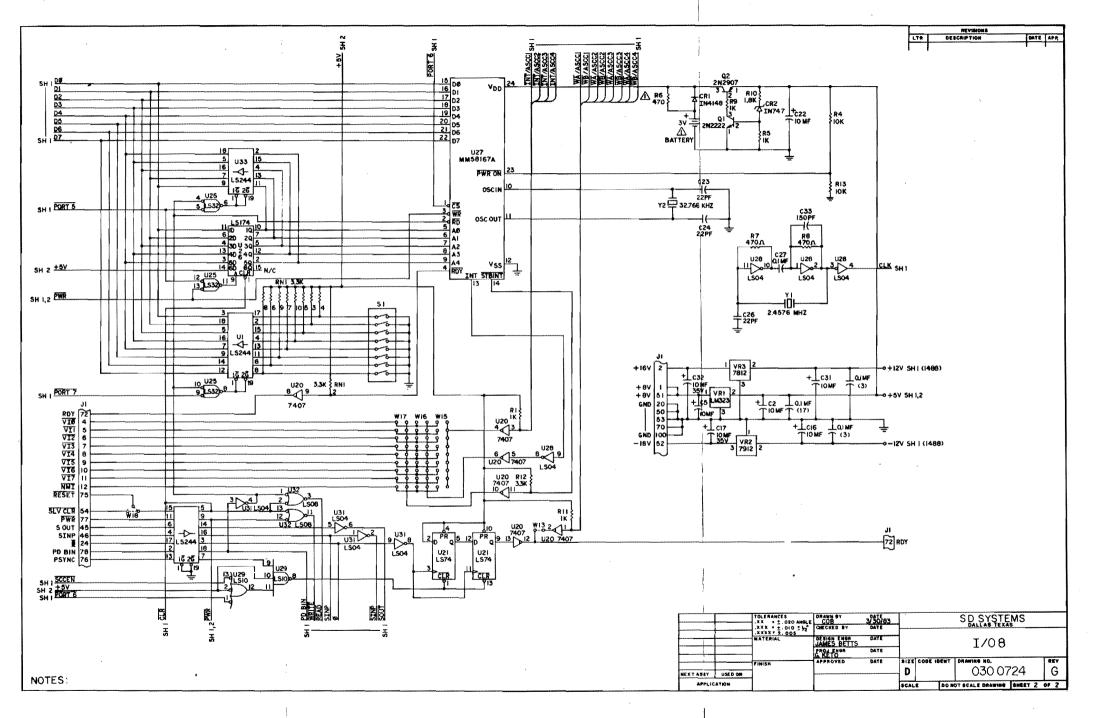

|   | J                     | SCHEMATIC                                                              | J-1               |

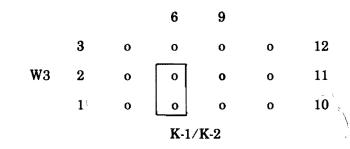

|   | K                     | JUMPER NUMBERING NOTATION                                              | <b>K</b> -1       |

| 4 |                       | ILLUSTRATIONS                                                          |                   |

|   | Figure                |                                                                        | Page              |

|   | No.                   | Title                                                                  | No.               |

|   | <b>2</b> -1           | I/O-8 BLOCK DIAGRAM                                                    | 2-2               |

|   | 3-1                   | ASYNCHRONOUS DATA CHARACTER                                            | 3-3               |

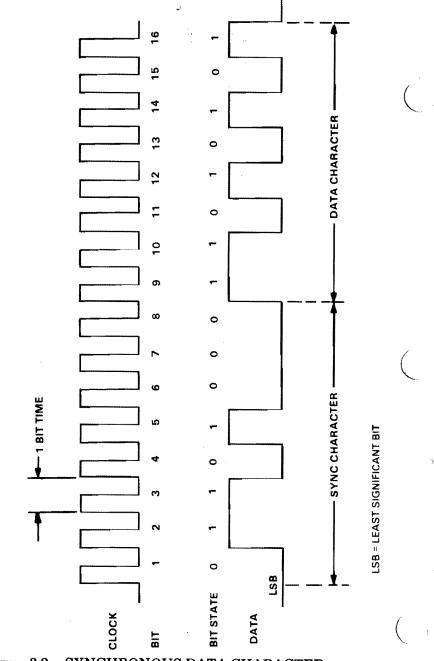

|   | 3-2                   | SYNCHRONOUS DATA CHARACTER                                             | 3-4               |

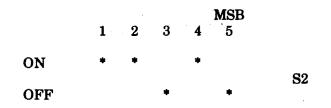

|   | 4-1                   | S2 SWITCH SETTING FOR ADDRESS A0H                                      | 4-2               |

|   | 4-2                   | SWITCH SETTING FOR THE 16 BIT                                          | 4.0               |

| ) | 4.9                   | ADDRESS 5C38H                                                          | 4-2               |

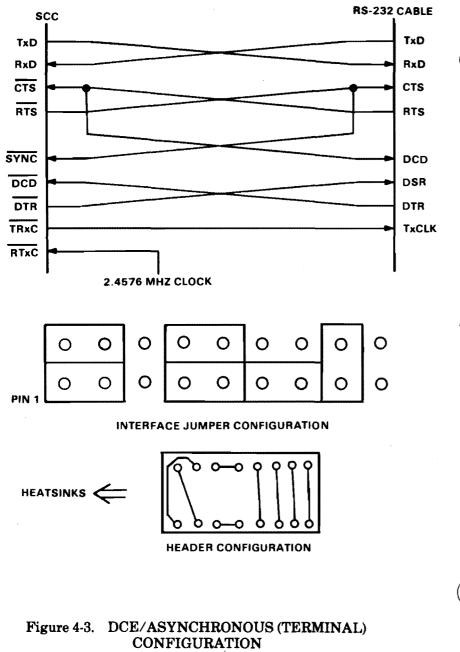

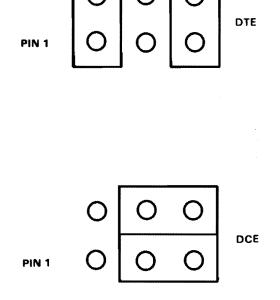

| / | 4-3                   | DCE/ASYNCHRONOUS (TERMINAL)<br>CONFIGURATION                           | 4-6               |

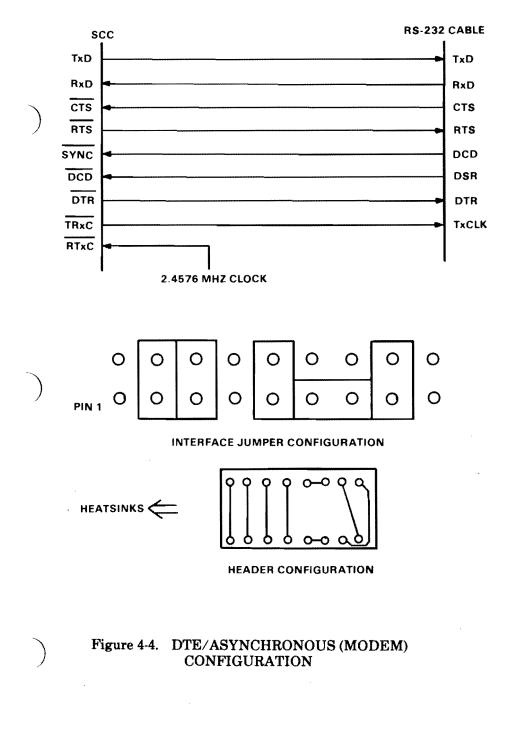

|   | 4-4                   | DTE/ASYNCHRONOUS (MODEM)                                               | 4-0               |

|   | - <b>TZ</b>           | CONFIGURATION                                                          | 4-7               |

|   |                       |                                                                        |                   |

. . .

# TABLE OF CONTENTS (Continued)

### **ILLUSTRATIONS--Continued**

| Figure<br>No. | Title                           | Page<br>No. | ( |

|---------------|---------------------------------|-------------|---|

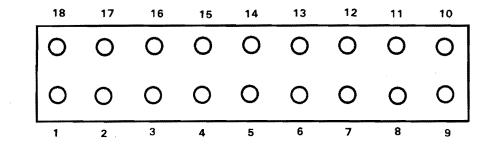

| 4-5           | INTERFACE JUMPER STRIP PIN      |             |   |

|               | NUMBERS                         | 4-8         |   |

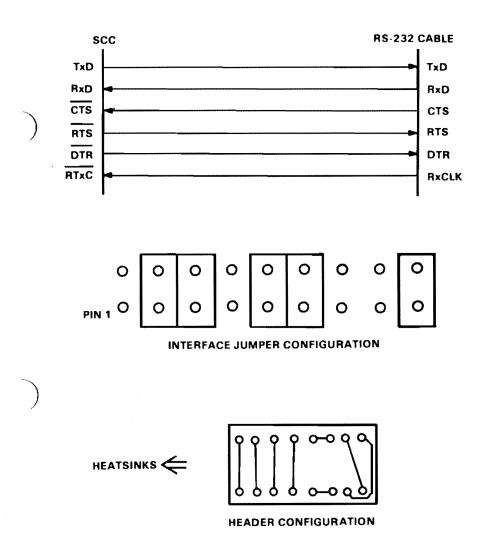

| 4-6           | JUMPER CONFIGURATIONS FOR PORTS |             |   |

|               | 2, 4, 6, & 8                    | 4-10        |   |

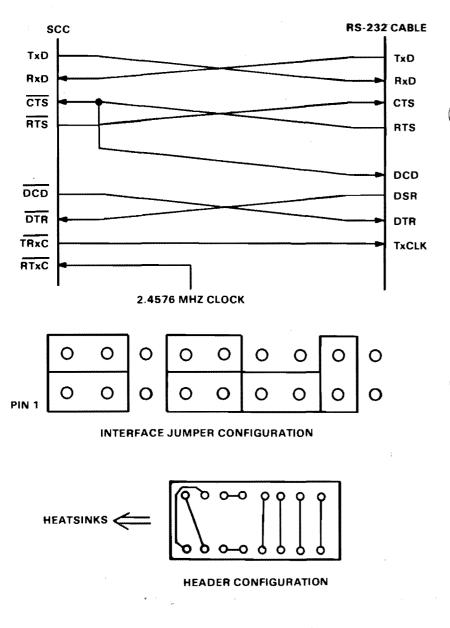

| 4-7           | DTE/SYNCHRONOUS CONFIGURATION   | 4-11        |   |

| 4-8           | DCE/SYNCHRONOUS CONFIGURATION   | 4-12        |   |

### TABLES

| Table<br>No. | Title                                  | Page<br>No. |   |

|--------------|----------------------------------------|-------------|---|

| 4-1          | <b>RS-232 SIGNALS SUPPORTED BY THE</b> |             |   |

|              | I/O-8                                  | 4-3         |   |

| 4-2          | CONFIGURATION JUMPERS                  | 4-4         |   |

| 4-3          | INTERRUPT JUMPER OPTIONS               | 4-13        | ( |

| 4-4          | PORT ADDRESS MAP                       | 4-14        |   |

| 4-5          | STATUS PORT FORMAT                     | 4-15        |   |

| 4-6          | BAUD RATE GENERATOR TIME               |             |   |

|              | CONSTANTS                              | 4-17        |   |

| 4-7          | RTC REGISTER FUNCTIONS AND             |             |   |

|              | ADDRESS CODES                          | 4-20        |   |

| 4-8          | REAL TIME COUNTER FORMAT               | 4-21        |   |

| 4-9          | INTERRUPT CONTROL AND INTERRUPT        |             |   |

|              | STATUS REGISTER FORMAT                 | 4-22        |   |

| 4-10         | RTC COUNTER AND RAM RESET              |             |   |

|              | FORMAT                                 | 4-23        |   |

|              |                                        |             |   |

1.0 GENERAL

The I/O-8 is an 8530/8531 based interface board which fully complies with the IEEE-696 specification for the S-100 bus. The I/O-8 operates as a Bus Slave under control of the IEEE-696 permanent or temporary Bus Master. The I/O-8 board is designed to provide serial communication capability from an S-100 computer to various Data Communications Equipment (DCE) or Data Terminal Equipment (DTE).

The following is a list of technical references applicable to the I/O-8:

IEEE-696 Bus Specification 8530 SCC Product Specification (Zilog) 8531 ASCC Product Specification (Zilog) 58167A RTC Product Specification (National) EIA- RS-232C Specification

1.1 FEATURES

The key features of the I/O-8 board are as follows:

1. Serial Ports

4 ports asynchronous DTE/DCE 4 ports synchronous/asynchronous DTE/DCE 8 I/O ports are addressable to any 8 port boundary in 64K

2. Baud Rate

Each channel software selectable, full duplex 50 to 19,200 in asynchronous mode using x16 internal clock

Up to 1Mbit/sec in synchronous mode using external clock

Up to 307,200 in synchronous mode using x1 on board internal clock (2.4576 mHz)

3. Data Bits

5, 6, 7, or 8 data bits/character Stop bits - 1, 1.5, 2 Clock rate - x1, x16, x32, x64 Parity - odd, even, or none Error detection - parity, overrun, CRC or framing Data encoding - NRZ, NRZI, FM1, FM0

4. Interrupts

Receiver ready All receive characters Special receive condition (parity error, framing error, overrun error, and end of frame in SDLC)

- 5. Real Time Clock With Battery Backup

- 6. Software Programmable Interrupt Rates

- 7. Standby Interrupt While Powered Down

- 8. Millisecond Through Month Counters

- 9. User Readable Switch

### SECTION II FUNCTIONAL DESCRIPTION

#### 2.0 GENERAL

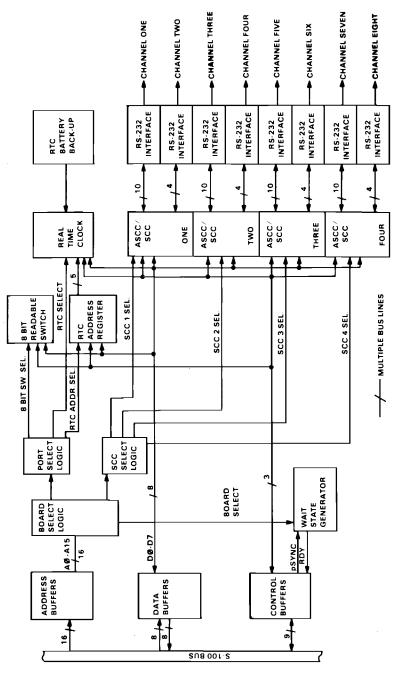

A functional block diagram of the I/O-8 board is shown in Figure 2-1. This section gives a brief description of each of the major blocks.

#### 2.1 SERIAL INPUT/OUTPUT

Eight full duplex serial communications channels are contained on the I/O-8.

2.1.1 Serial Communications Controller (SCC/ASCC)

The Z8530A or Z8531A Serial Communications Controller (SCC) is used to interface and control the serial ports. The Z8530A SCC is used for synchronous or asynchronous communications while the Z8531A ASCC will perform asynchronous communications only. Both of these chips have an on-board programmable baud rate generator, complete interrupt control, and four different ways of encoding data. The SCC can also support byte-oriented and bitoriented synchronous protocols including SDLC, HDLC, and Bisync.

The Z8030/Z8530 SCC Serial Communications Controller Technical Manual describes the options that can be selected under software control. A partial list follows:

- \* 5, 6, 7 or 8 bits/character

- \* even, odd, or no parity

- \* 1, 1-1/2 or 2 stop bits

\* CRC generation/checking (sync modes only)

\* Polled I/O or Interrupt operation

\* Parity, overrun, and framing error detection

#### 2.1.2 Serial Port Interface

i i coloriane

The SCC to RS-232 interface is performed by the common MC1488 line driver and MC1489 line receiver. Four ports have a complete interface (TxD, RxD, CTS, RTS, DTR, DSR, DCD, RxCLK, TxCLK, and CLK) allowing synchronous/asynchronous communication with a terminal or modem (DCE or DTE). A header is included on the full ports to make the switch from terminal to modem easier in most cases. The remaining four ports support asynchronous only using four signals (TxD, RxD, CTS, and RTS). The RxD and TxD lines can be swapped to allow a limited conversion for modem use.

(

#### 2.1.3 SCC Interrupts

Each of the eight I/O channels can generate three types of interrupts:

- 1) Transmit

- 2) Receive

- 3) External/Status

Transmit interrupt indicates the transmit buffer is empty. Receive interrupts are of three types:

- 1) First receive character or special receive condition

- 2) All receive characters or special receive condition

- 3) Special receive condition only (parity error, framing error)

External/Status interrupts will be generated by various status or error conditions including:

- 1) Clear To Send (CTS) transition

- 2) Data Carrier Detect (DCD) transition

- 3) Transmit underrun

- 4) Zero baud rate count

All three types of channel interrupts are sent on one interrupt line shared with all eight channels. A jumper strip is provided to allow the serial I/O interrupt line to be connected to any of the bus interrupt lines (Vectored Interrupt 0 to 7 or the Non-Maskable Interrupt).

2.2 REAL TIME CLOCK (RTC)

The I/O-8 uses the 58167A Real Time Clock chip featuring software programmable interrupt rates, battery backup, 56 bits of RAM, and clock counters.

2.2.1 RTC Counters and RAM

The Real Time Clock provides time and day counters and 56 bits of RAM. Nine counters are available: milliseconds, hundredths of seconds, tenths of seconds, seconds, minutes, hours, day of week, day of month, and months. The RAM can be used for storage while the system is powered down or for generating interrupts at preset times.

#### 2.2.2 RTC Battery Backup

An on-board battery provides power to the real time clock and standby interrupt function during system power down. Accurate time can be kept for up to six months in power down mode (dependent upon temperature and battery cycle life).

#### 2.2.3 RTC Interrupts

Two types of interrupts can be generated by the Real Time Clock: the standby interrupt and a general interrupt output. Both interrupts can be programmed for fixed interrupt rates or for a preset time. Also, both interrupts can be independently connected through jumper strips to any bus interrupt line (Vectored Interrupt 0 to 7 or the Non-Maskable Interrupt).

The standby interrupt is used when the host system is powered down and the RTC is battery powered. This interrupt signals another device on the bus (with its own power source) that a set time has passed. Two possible uses would be to have circuitry that would power up the computer when this interrupt occurred or to signal the computer on power up that a preset time has passed.

The general interrupt output is used during normal operation when the host system is powered up. A possible use would be in a multiuser time sharing system. Each time an interrupt occurred it would signal the host system to service a different user.

#### 2.3 BOARD SELECT AND PORT DECODE LOGIC

Eight of the host processor's Input/Output ports are used by the I/O-8. The SCCs require four ports (two for data and two for control), the SCC select register uses one, the RTC address select register uses one, the RTC uses one, and the eight bit readable switch uses one. The address for this block of ports can be placed at any eight byte boundary in 64K. This means the address could be placed at 0 or 8 but not at 1, 2, 3, 4, 5, 6, or 7 because these locations are not evenly divisible by eight.

The board select signal is generated by comparing the S-100 address lines with five or 13 user set switches. The number of switches depends on whether the host processor has an eight bit or a 16 bit I/O address. For example, a Z80 based processor would use eight bits and a 68000 processor would use sixteen bits. A three pin jumper strip is

used to switch between the two modes of addressing. After a board select address is found, the remaining three address bits are tested to determine which port is being accessed. A chip select signal is then generated to enable the proper port.

### 2.4 SCC SELECT REGISTER

To conserve on the number of Input/Output ports needed by the I/O-8, a register was added to select only one SCC at a time. Without this register, 16 I/O ports would have been needed to control the SCCs. With this register five I/O ports are used, a saving of 11 ports. Outputting the SCC's number (0-3) to this register will cause the two data and two control registers of the selected SCC to be placed at the first four ports.

#### 2.5 RTC ADDRESS SELECT/STATUS REGISTER

As an additional saving on the number of Input/Output ports used, a register was added to select a Real Time Clock register. Any RTC register can be written to or read from by first outputting its number (0 - 32) to the RTC Address Select Register and then accessing the RTC port. Using this technique, the host processor I/O ports needed were reduced from 32 to only two.

The function of the RTC Address Select Register changes slightly during a read operation. As expected, the selected RTC register number is contained in the lower five bits. But in a read operation the upper two bits contain the number of the selected SCC. This allows the complete status on which SCC is selected and which RTC register is selected to be determined by reading the one port.

#### 2.6 EIGHT BIT SWITCH PORT

An additional feature of the I/O-8 is a readable switch port. The user assigns a function to each of the eight switches and through the software can determine how the board is configured. An example of its use is in a system that has mixed synchronous and asynchronous channels. The user decides that each bit will correspond to an I/O-8 channel. If the switch is off, the channel will be synchronous and, if on, the channel is asynchronous. The software drivers are then written to read the switch port and initialize each channel to the desired configuration. When it is necessary to add another synchronous port, the switch can be changed and the software will automatically initialize the channel properly.

### 2.7 WAIT STATE GENERATOR

To synchronize the SCCs and Real Time Clock with the host processor a wait state generator has been added. Any access to the SCCs will automatically have two wait states inserted and any access to the Real Time Clock will have four wait states inserted. The SCC Select Register, RTC Address Select Register, and Eight Bit Switch Port can operate at higher speeds and do not need any wait states.

### SECTION III THEORY OF OPERATIONS

#### 3.0 GENERAL

To make the I/O-8 board more understandable to the end user, the following subsections describe the general operation theory behind the I/O-8. Topics discussed are serial communications in synchronous and asynchronous formats and the need for DCE and DTE interfaces.

#### 3.1 SERIAL COMMUNICATIONS

In serial communications the data bytes to be transmitted are converted from the parallel form in the computer to a serial form for transmission on a single wire. The RS-232-C standard was written to define the serial interface.

#### 3.1.1 DCE And DTE

Two types of RS-232 serial devices exist: Data Communications Equipment (DCE) and Data Terminal Equipment (DTE). These types are necessary since the RS-232-C standard defines signals on the connecting cable to be unidirectional. Obviously the Transmit Data (TxD) pin of one device must be connected to the Receive Data (RxD) pin of the other device. To do this the first device (DTE) must have its TxD pin connected to the RS-232 TxD line, and the second device (DCE) must have its RxD pin connected to the RS-232 TxD line. As a result the two devices that are being interfaced must be of opposite types--one DTE and one DCE. The DTE device always has its interface pins connected to the RS-232 line with the same name. The interface to make a device DCE is not as straightforward. Each line in the RS-232 specification is paired with another line with the same general function (i.e. TxD-RxD, RTS-CTS, DTR-DSR). A DCE interface is made by matching the cable lines with the SCC line that is in the function pair.

3.1.2 Synchronous And Asynchronous Communications Formats

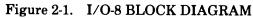

The main difference between synchronous and asynchronous communications formats is in the timing used for receiving information bits. Synchronous transmissions use a separate clock signal for indicating when another bit is to be received, while asynchronous transmissions use a start bit to signal the beginning of a data character. Figure 3-1 shows the format of an asynchronous data character, and Figure 3-2 shows the format of a synchronous data character. Both of these formats approximately correspond to the voltage waveform expected on the RS-232 Transmit Data (TxD) and Receive Data (RxD) lines.

Before an asynchronous data character is transmitted, the line is always in a high (1) state. The arrival of a start bit signals the beginning of a data character, and a fixed number of data bits along with a parity bit will be received. The end of a data character is marked by 1, 1.5, or 2 stop bits. After the stop bits, another start bit can be transmitted or the line can return to its idle state. The rate that data bits are received or transmitted in asynchronous mode is called the baud rate. The SCC generates its own baud rate clock to sample incoming data at the proper rate. Figure 3-2 shows an example of a monosynchronous data transmisson. Transitions on the CLOCK line indicate that another bit is to be sampled. After each bit is received, a comparison is made for a match with the sync character programmed in the SCC. The example in Figure 3-2 uses a 01101000B for the sync character. After the sync character is recognized, all subsequent bits are assumed to be data and are placed in the receive buffer. Because of the lack of framing bits, synchronous transmissions are more efficient than asynchronous transmissions.

(

3-3

Figure 3-2. SYNCHRONOUS DATA CHARACTER

1

3-4

#### 4.0 GENERAL

The I/O-8 can be configured to operate in any of several modes including: synchronous, asynchronous, Data Terminal Equipment (DTE), or Data Communications Equipment (DCE). This section describes the set-up procedure for these modes and the procedures for programming the Serial Communications Controllers (SCC) and the Real Time Clock (RTC).

#### 4.1 BOARD ADDRESSING OPTIONS

The I/O-8 requires eight consecutive ports of the host processor's input/output ports for communicating with the SCCs and RTC. The address of these ports can be 8 or 16 bits long depending on the host processsor. Jumper W14 is used to choose between the two address lengths. Switches S2 and S3 then determine the address of the first port used on the I/O-8.

For most microprocessors, the input/output port addresses are eight bits long (SBC-200). Jumper W14 should be on pins one and two for this case. Switch S2 should have the five most significant bits of the address. With the card edge connector pointing down, address bit seven will be on the right. Switch S3 can be ignored for an eight bit port address.

Example: Initialize the I/O-8 board address to A0H for use with a Z80 processor.

A Z80 has an eight bit I/O address length; so W14 should be on pins one and two. The hexadecimal address A0H is equivalent to 10100000B in binary (consult the Appendix called Base Conversions). Ignore the rightmost three bits and place the remaining five bits on switch S2. For a zero in the address, turn the corresponding switch to the on position and, for a one, turn the switch to the off position. The switch setting for address A0H is shown in Figure 4-1. From the figure, note the order that the bits were placed onto S2.

#### Figure 4-1. S2 SWITCH SETTING FOR ADDRESS A0H

If the host processor being used has 16 bit I/O port addresses (SBC-68000), jumper W14 should be on pins two and three. Switches S2 and S3 will have the 13 most significant bits of the address.

**Example:** Initialize the I/O-8 board address to 5C38H for use with a 68000 processor.

Since the 68000 processor has I/O port addresses that are 16 bits long, place jumper W14 on pins two and three. Converting the hexadecimal address 5C38H to binary gives 0101110000111000B (consult the Appendix called Base Conversions). Place the left eight bits on S3 and the next five bits on S2. Ignore the rightmost three bits. For a zero in the address, turn the corresponding switch to the on position and, for a one, turn the switch to the off position. Figure 4-2 gives the switch setting for address 5C38H. From the figure, note the order that the bits were placed onto S2 and S3.

|             |   | 1 | 2 | 3    | 4 | 5            |   |     |                |

|-------------|---|---|---|------|---|--------------|---|-----|----------------|

| ON          |   |   |   |      | * | ٠            |   |     | S2             |

| OFF         |   | * | * | ٠    |   |              |   |     | Address = 38H  |

|             |   |   |   |      |   |              |   | MSI | B              |

|             | 1 | 2 | 3 | 4    | 5 | 6            | 7 | 8   |                |

| ON          | • | * |   |      |   | *            |   | *   | <b>S</b> 3     |

| OFF         |   |   | • | *    | * |              | ٠ |     | Address = 5CH  |

| Figure 4-2. |   |   |   | H SE |   | NG F<br>C38H |   | THE | 16 BIT ADDRESS |

|             |   |   |   |      |   |              |   |     |                |

#### 4.2 SERIAL INTERFACE OPTIONS

The I/O-8 has a flexible serial interface to allow it to communicate with a variety of devices. The following subsections describe the configurations for a terminal (DCE) or modem (DTE) and synchronous or asynchronous communications.

4.2.1 Terminal Or Modem Configuration (DCE or DTE)

RS-232 devices fall into two categories: Data Communications Equipment (DCE) and Data Terminal Equipment (DTE). The device being interfaced determines whether the I/O-8 should be configured for DCE or DTE. A terminal or printer needs a DCE interface and a modem needs a DTE interface. Consult the owner's manual for the device to determine which interface is needed.

All channels on the I/O-8 can support a DCE or DTE interface, but four partial channels (2, 4, 6, and 8) have only four signals available. When choosing which channel to use, the number of signals required must be allowed for. A terminal usually needs only two signals (RxD and TxD); so any of the eight channels can be used. A printer outputs a signal to indicate when it is ready to receive data, and may need certain other signals to be at a known level. One of the four full interface channels (1, 3, 5, or 7) has to be used in this case. Table 4-1 lists the signals available on each channel.

#### Table 4-1. RS-232 SIGNALS SUPPORTED BY THE I/O-8

|       | Signal Name           | Channels<br>(1,3,5,7) | Channels<br>(2,4,6,8) |

|-------|-----------------------|-----------------------|-----------------------|

| TxD   | (Transmit Data)       | Yes                   | Yes                   |

| RxD   | (Receive Data)        | Yes                   | Yes                   |

| CTS   | (Clear To Send)       | Yes                   | Yes*                  |

| RTS   | (Request To Send)     | Yes                   | Yes*                  |

| DCD   | (Data Carrier Detect) | Yes                   | No                    |

| DSR   | (Data Set Ready)      | Yes                   | No                    |

| DTR   | (Data Terminal Ready) | Yes                   | No                    |

| RxCLK | (Receive Clock)       | Yes                   | No                    |

|       | (Transmit Clock)      | Yes                   | No                    |

| CLK   | (Clock)               | Yes                   | No                    |

| PGND  | (Protective Ground)   | Yes                   | Yes                   |

| SGND  | (Signal Ground)       | Yes                   | Yes                   |

\* A special cable is needed to use this signal in DCE mode.

The procedure for converting a channel from DCE to DTE or DTE to DCE varies depending on whether the channel interface is full or partial. Changing a full interface can usually be done by reversing a header. For the cases that use more signals in the interface (such as a printer), two jumper strips also have to be changed. A partial interface needs only one jumper strip changed to make the conversion. Table 4-2 lists the header, jumper strips, and cable connector associated with each channel.

#### Table 4-2. CONFIGURATION JUMPERS

| Channel Number<br>(Cable Connector) | Interface<br>Jumpers | Sync<br>Jumper | Header     |

|-------------------------------------|----------------------|----------------|------------|

| 1 ( <b>J</b> 2)                     | <b>W</b> 1           | <b>W</b> 10    | <b>H</b> 1 |

| 2 (J3)                              | W2                   |                |            |

| 3 (J4)                              | <b>W</b> 3           | W11            | H2         |

| 4 (J5)                              | W4                   |                |            |

| 5 (J6)                              | W5                   | W9             | H3         |

| 6 (J7)                              | W6                   |                |            |

| 7 (J8)                              | W7                   | W12            | H4         |

| 8 (J9)                              | W8                   |                | **         |

# NOTE: Use the Parts Placement Diagram Appendix to locate the headers and jumper strips on the I/O-8.

#### 4.2.2 Asynchronous Communications

After choosing a DCE or DTE interface the communication format (synchronous or asynchronous) must also be chosen. The following subsections describe asynchronous communications on the I/O-8. Synchronous communications are described in Section IV, Subsection 4.2.3.

4.2.2.1 Full Interface Channels (1, 3, 5, 7)

At this point the type of interface (DCE or DTE) and the communications format (synchronous or asynchronous) have been chosen. This subsection describes how to set up a serial channel for DCE/asynchronous or DTE/asynchronous modes.

In most cases, such as terminals, the interface type can be chosen by how the header is inserted. From Table 4-2 find the header number for the channel being used (i.e. the header for Channel 7 is H4). Insert the header with the four straight wires pointing away from the heatsinks for a DCE interface (Figure 4-3). Insert the header with the four straight wires pointing toward the heatsinks for a DTE interface (Figure 4-4). The headers shown in Figures 4-3 and 4-4 may not be the same as on an early revision I/O-8 board. Always use the four parallel wires to determine the orientation of a header.

If the headers alone are being used to configure the serial channels, one jumper must be installed on the interface jumper strip. Find the jumper strip for the channel being configured from Table 4-2 (i.e. for Channel 3 the interface jumper strip is W3). Place a jumper on pins 6 and 7 of the interface jumper strip. Figure 4-5 shows the pin numbers of the interface jumper for Channels 1, 3, 5, and 7.

When a complete serial channel is needed the interface jumper strip and sync jumper have to be completely configured in addition to the header. Find the interface jumper strip from Table 4-2 for the channel being configured. If a DTE interface is being used, copy the jumper configuration shown in Figure 4-4 onto the interface jumper strip. If a DCE interface is being used, copy the jumper configuration shown in Figure 4-3 onto the interface jumper strip. While copying the jumper configurations, always hold the I/O-8 board with the card edge connector pointing down. This puts pin 1 of the interface jumpers in the lower lefthand corner. From Table 4-2 find which sync jumper is with the serial channel being configured. For the asynchronous mode, place a jumper on the sync jumper strip.

Example: Convert Channel 5 to work with a terminal.

A terminal would need a DCE/asynchronous interface. Inserting header H3 with the correct orientation should be sufficient but, for this example, a complete configuration will be done. Copy the jumper configuration from Figure 4-3 onto W5. Jumper strip W5 has been chosen because it is the interface jumper for Channel 5 (Table 4-2). Insert header H3 with the four straight wires pointing away from the heatsinks (Figure 4-3). Since the terminal is asynchronous, place a jumper on W9.

Figure 4-5. INTERFACE JUMPER STRIP PIN NUMBERS

4-8

4.2.2.2 Partial Interface Channels (2, 4, 6, 8)

Four channels on the I/O-8 have a partial serial interface that is intended to be used mainly with terminals. These channels are also limited to asynchronous communications only. Configuring a partial channel is done with one 2x3 jumper strip. The interface jumper strip associated with each channel is shown in Table 4-2 (i.e. for Channel 4 the interface jumper strip is W4). Hold the I/O-8 board with the card edge connector pointing down. This puts pin 1 of the interface jumper strip in the lower lefthand corner. Choose which interface type (DCE or DTE) is needed and copy the corresponding jumper configuration from Figure 4-6 onto the interface jumper strip.

Example: Convert channel number 2 to work with a modem.

A modem needs a DTE interface. Also, the modem must be asynchronous. (Use Channel 1, 3, 5, or 7 if the modem is synchronous.) Copy the DTE jumper configuration in Figure 4-6 onto W2.

#### 4.2.2.3 Printers

The four full interface channels of the I/O-8 can be configured to work with a serial asynchronous printer. Most printers use one RS-232 line to indicate when the printer is ready to receive data. Use the printer owner's manual to determine which line is used for printer busy. Configuring the I/O-8 involves setting the header to DCE mode and connecting the printer busy line to the DCD input. The I/O-8 CP/M software drivers have been written to use the DCD input for printer busy. If special software drivers have been written, any of the input lines could be used.

#### 4.2.3 Synchronous Communications

When using Z8530 SCCs, the I/O-8 can support several synchronous communication protocols on the full interface channels (1, 3, 5, and 7). As in asynchronous communications, a DCE or DTE type interface must be chosen. The main difference between an asynchronous configuration and a synchronous configuration is the clock sources. Either the I/O-8 or the device being interfaced must generate all of the clocks. Figures 4-7 and 4-8 show two sample synchronous configurations. In the DTE/synchronous configuration (Figure 4-7) the clock is generated by the interfaced device (i.e. synchronous modem) and received by the SCC at its RTxC pin. In the DCE/synchronous configuration (Figure 4-8) the baud rate clock is generated from the on-board 2.4576 mHz oscillator and transmitted to the interfaced device using the RS-232 CLK line. These samples were chosen to satisfy the requirements of most synchronous devices. Consult the owner's manual to determine if the device needs a different arrangement of clocks. In addition to configuring the channel, a software driver has to be written that will operate the SCC in synchronous mode.

### Figure 4-6. JUMPER CONFIGURATIONS FOR PORTS 2, 4, 6, AND 8

Figure 4-7. DTE/SYNCHRONOUS CONFIGURATION

· · · · · · ·

Figure 4-8. DCE/SYNCHRONOUS CONFIGURATION

Configuring a channel is done in the same manner for synchronous modes as in asynchronous modes. After choosing which channel to use (1, 3, 5, or 7), find the two jumper strips and the header for the channel from Table 4-2. Use Figure 4-7 or 4-8 depending on which interface type (DCE or DTE) has been chosen and insert the header with the orientation shown. Hold the I/O-8 board with the card edge connector pointing down and copy the jumper configuration onto the interface jumper strip (Table 4-2). Since the board is running in synchronous mode, a jumper should not be on the sync jumper strip. Find the sync jumper strip number from Table 4-2 and check to see that a jumper is not on it.

#### 4.3 MISCELLANEOUS OPTIONS

Additional features of the I/O-8 include options for interrupts, reset compatibility, and the SCC wait function.

#### 4.3.1 Interrupt Options

The I/O-8 board contains three interrupt sources: SCC, Real Time Clock, and the standby RTC. Each of the sources can be placed on any of nine S-100 interrupt lines (Vectored Interrupt 0 to 7 and Non-Maskable Interrupt). Table 4-3 shows which jumpers to insert to connect a given interrupt source to a given interrupt line.

#### Table 4-3. INTERRUPT JUMPER OPTIONS

|      | SCC<br>INTERRUPTS | RTC<br>INTERRUPTS | RTC STANDBY<br>INTERRUPTS |

|------|-------------------|-------------------|---------------------------|

| VI0* | W15-1             | W16-1             | W17-1                     |

| VI1* | W15-2             | W16-2             | W17-2                     |

| VI2* | W15-3             | W16-3             | W17-3                     |

| VI3* | W15-4             | W16-4             | W17-4                     |

| VI4* | W15-5             | W16-5             | W17-5                     |

| VI5* | W15-6             | W16-6             | W17-6                     |

| VI6* | W15-7             | W16-7             | W17-7                     |

| VI7* | W15-8             | W16-8             | W17-8                     |

| NMI* | W15-9             | W16-9             | W17-9                     |

### 4.3.2 RESET/SLAVE CLR Option

The IEEE-696 S-100 specification requires that all bus slaves be reset using the SLAVE CLR\* signal. Older boards usually do not generate SLAVE CLR\* but will reset bus slaves using the RESET\* signal. A jumper has been supplied to allow the I/O-8 to be reset using either the RESET\* or SLAVE CLR\* signal. If the host processor meets the IEEE-696 specification, place a jumper on pins two and three of W18; otherwise, place a jumper on pins one and two.

4.3.3 SCC Wait Line Option

A feature of the SCCs is a wait line that can signal the host processor when it is ready for more data. This makes it possible to use the Z80 OTIR instruction to transmit a long string of data. To enable this function, place a jumper on W13.

#### 4.4 PORT ADDRESS MAP

The input/output port map for the I/O-8 is shown in Table 4-4.

#### Table 4-4. PORT ADDRESS MAP

| Port Address | Channels                                       |

|--------------|------------------------------------------------|

| 000*         | Channel B - control (R/W)                      |

| 001          | Channel A - control (R/W)                      |

| 010          | Channel B - data (R/W)                         |

| 011          | Channel A - data (R/W)                         |

| 100          | SCC select (W)                                 |

| 101          | RTC register select - SCC status               |

|              | (R)                                            |

| 110          | RTC Data (R/W)                                 |

| 111          | Readable switch                                |

|              | 000*<br>001<br>010<br>011<br>100<br>101<br>110 |

\* User supplies upper 13 bits with switches S2 and S3. NOTE: The addresses given are the factory settings.

- Port 0 This port is used for programming Channel B of the selected SCC.

- Port 1 This port is used for programming Channel A of the selected SCC.

- Port 2 Data transmitted or received by Channel B of the selected SCC is sent through this port.

- Port 3 Data transmitted or received by Channel A of the selected SCC is sent through this port.

- Port 4 An SCC is selected by outputting its number (0-3) to this port. The six most significant bits are ignored.

- Port 5 This port will contain the five bit address of a Real Time Clock register. An input will give the RTC address in the lower five bits and the number of the selected SCC in the upper two bits (the format is shown in Table 4-5).

- Port 6 This port is for I/O to the RTC register that was selected by writing to port 5.

- Port 7 An eight bit readable switch is at this port. The value on this switch can be used to determine the system configuration.

# Table 4-5. STATUS PORT FORMAT

| D7             | D6   | D5      | D4             | D3         | D2      | D1         | D0         |

|----------------|------|---------|----------------|------------|---------|------------|------------|

| CS2            | CS1  | Х       | A4             | <b>A</b> 3 | A2      | <b>A</b> 1 | <b>A</b> 0 |

|                |      |         |                |            | 1       |            |            |

| V              |      |         | RTC            | Regis      | ster Ad | aress      |            |

| ↓<br>↓<br>00 = | SCCI | l (Port | RTC<br>ts 1/2) | -          | ster Ad | laress     |            |

|                |      |         |                |            | ster Ad | laress     |            |

| 01 =           | SCC2 | 2 (Por  | ts 1/2)        |            | ster Ad | laress     |            |

### 4.5 SCC PROGRAMMING

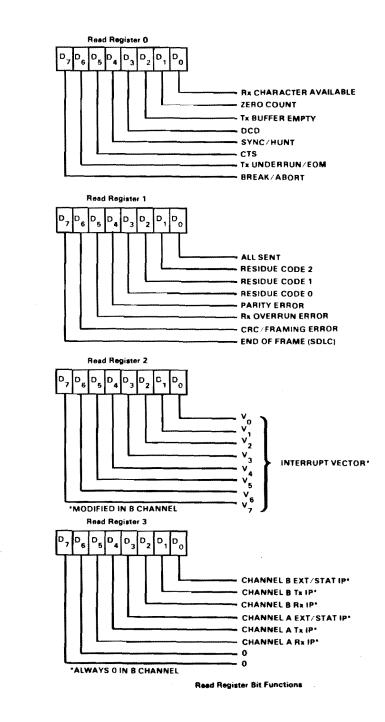

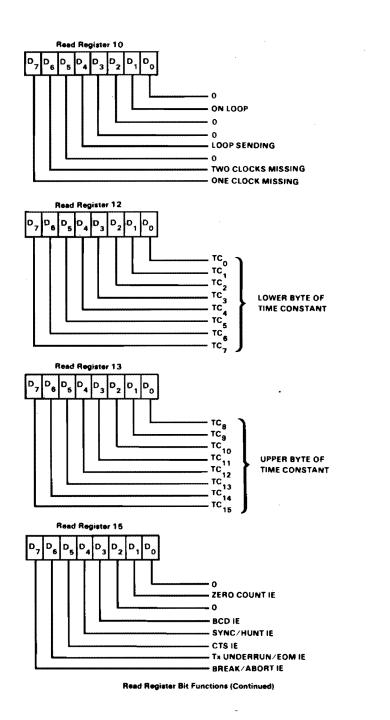

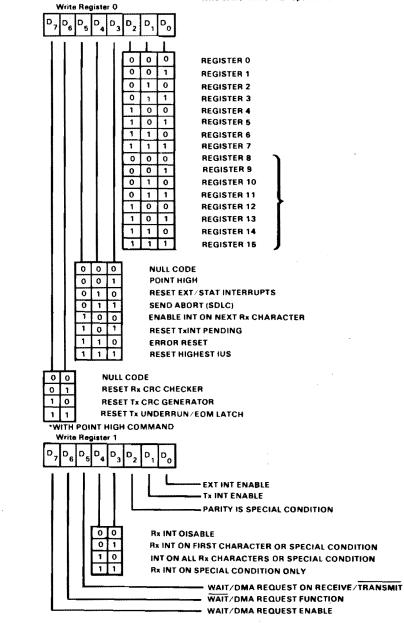

The Zilog 8530 Serial Communications Controller (SCC) contains 13 write registers for channel configuration and eight read registers for channel status. Four input/output ports are used on the I/O-8 to communicate with the SCCs. Two ports are for control (A0H and A1H) and directly communicate with the SCC register set for each serial channel. The remaining two ports (A2H and A3H) are used for transmitting and receiving data from the serial channels. See Section IV, Subsection 4.4 for a description of each port used by the SCCs.

Programming an SCC register is done in two operations. A write requires two write operations, and reading a register requires a write and a read. The first write is always to write register 0 (WR0) and contains three bits which select the next register to be accessed. The second operation (read or write) uses the register selected by the first write. The pointer bits are automatically cleared after the second operation so that WR0 and RR0 can be accessed again.

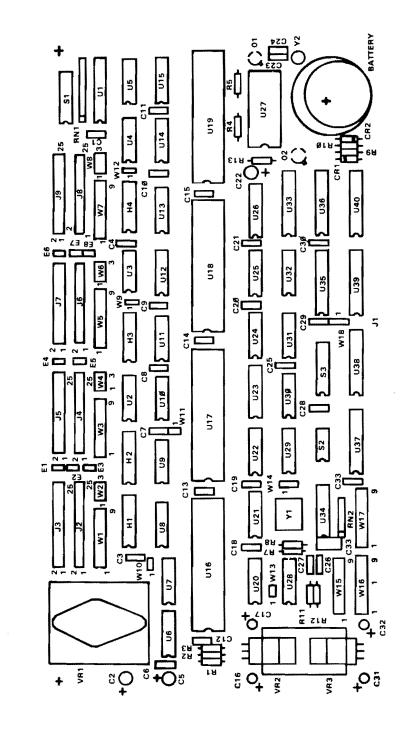

4.5.1 Asynchronous SCC Initialization

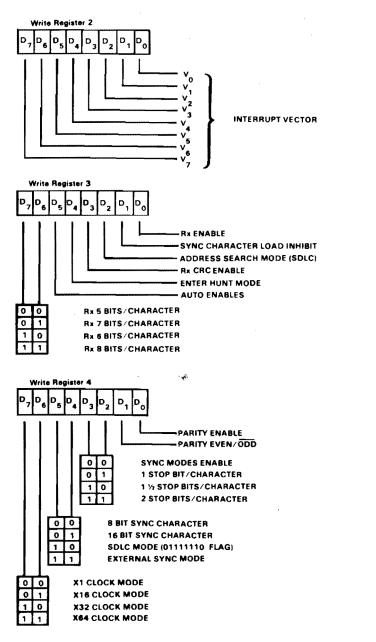

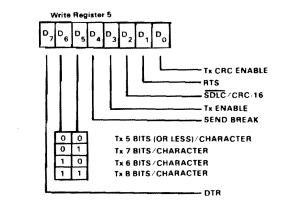

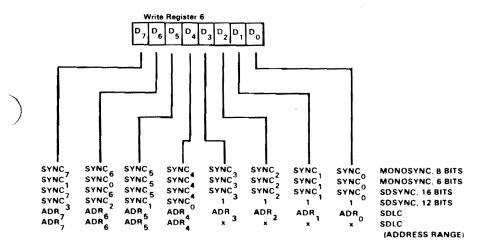

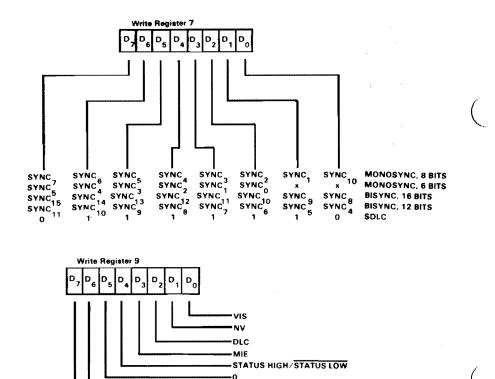

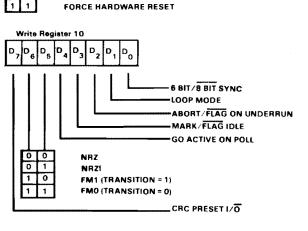

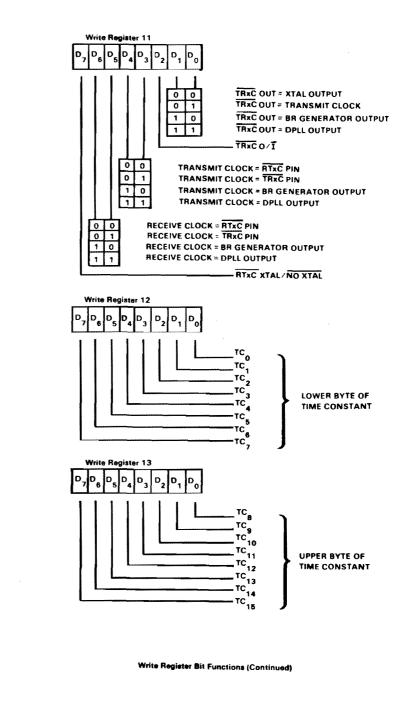

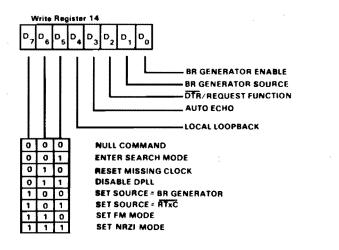

Seven of the SCC internal registers are used for asynchronous mode initialization (WR3, WR4, WR5, WR11, WR12, WR13, and WR14). Additional registers would be needed if interrupts were used. An example of the initialization routine described here is given in Section IV, Subsection 4.5.2. Also, the SCC Registers Appendix contains the format of all SCC registers.

The first register to be programmed is WR4. The bits in this register control parity, number of stop bits, and clock multiplier. In the example, parity is disabled, a x16 clock is used, and one stop bit is used. Storing a 44H in this register sets the chosen parameters (compare the 44H with register format in SCC Registers Appendix to see how the modes were selected). The second register to be programmed is WR3. Write register 3 contains bits for receiver enable, Auto Enables, and receive bits/character. The example uses C1H to enable the receiver, disable Auto Enables, and receive eight bits/character. WR5 sets transmit bits/character, transmitter enable, RTS, and DTR. The RTS and DTR bits directly control the corresponding RS-232 signals. Having a 1 in the DTR bit sets the RS-232 DTR high, and having a 0 does the converse. The example uses EAH to set the DTR and RTS signals high, enable the transmitter, and transmit 8 bits/character.

The remaining four registers are used to set the baud rate generator parameters. WR12 and WR13 contain the baud rate time constants. The values stored here are used to initialize a counter that determines the rate that data is transmitted or received. Table 4-6 lists the time constants needed to generate standard baud rates. WR11 determines the sources for the receive clock and transmit clock. Storing a 56H here causes the baud rate generator to be used for the receive and transmit clocks. Storing a 01H in WR14 enables the baud rate generator and sets the clock source for the BRG to the RTxC pin (2.4576 mHz oscillator). The BRG clock source could also be the host processor's system clock by storing a 03H in WR14.

### Table 4-6. BAUD RATE GENERATOR TIME CONSTANTS

NOTE: The following values are given for the x16 clock using the on-board 2.4576 mHz clock

|   | BAUD<br>RATE | SCC REG 0CH<br>(LOW BYTE) | SCC REG 0DH<br>(HIGH BYTE) | ERROR<br>(%) |

|---|--------------|---------------------------|----------------------------|--------------|

| / | 50           | FEH                       | 05H                        | 0            |

|   |              |                           |                            | •            |

|   | 75           | FEH                       | 03H                        | 0            |

|   | 110          | 68H                       | 02H                        | +0.03        |

|   | 134.5        | 39H                       | 02H                        | 0            |

|   | 150          | FEH                       | 01H                        | 0            |

|   | 300          | FEH                       | 00H                        | 0            |

|   | 600          | 7EH                       | 00H                        | 0            |

|   | 1200         | 3EH                       | 00H                        | 0            |

|   | 1800         | 29H                       | 00H                        | -0.80        |

|   | 2400         | $1\mathbf{EH}$            | 00H                        | 0            |

|   | 3600*        | 13 <b>H</b>               | 00H                        | +1.80        |

|   | 4800         | 0EH                       | 00H                        | 0            |

|   | 7200*        | <b>09H</b>                | 00H                        | -3.70        |

|   | 9600         | 06H                       | 00H                        | 0            |

| ) | 19200        | 02H                       | 00H                        | 0            |

| 1 |              |                           |                            |              |

\* These baud rates are approximations as shown by the percentage of error.

4.5.2 Asynchronous Programming Example

ASYNCHRONOUS SCC PROGRAMMING EXAMPLE

### FOR INSTRUCTIONAL PURPOSES ONLY

Consult the following manuals for further information on SCC programming. Both manuals are from Zilog.

Z8030/Z8530 Serial Communications Controller Technical Manual Z8530 and Z8030 SCC Initialization: A Worksheet and an Example

The port addresses used are for the standard factory settings.

| ld  | a,00h   | ; Select SCC number one |

|-----|---------|-------------------------|

| out | (a4h),a |                         |

4-17

|                | ld             | a,a1h                                 | ; Program Channel A                                                                                             |   |

|----------------|----------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|---|

|                | ld             | а,атп<br>С,а                          | , Program Onamier Age - Solg                                                                                    |   |

|                | ld             | b,0eh                                 | a start | i |

|                | ld             | h1,sccinit                            |                                                                                                                 | ( |

|                | otir           | 111,80011110                          | ; output initialization table                                                                                   |   |

| ÷              | 0011           |                                       | ; to control port of Ch. A                                                                                      |   |

|                |                |                                       |                                                                                                                 |   |

| <b>Frans</b> r | nit/ Re        | eceive routine                        |                                                                                                                 |   |

|                |                |                                       | μ <sup>α</sup> λ <sup>1</sup> α.                                                                                |   |

| next:          | in             | a,(a1h)                               | ; Check for received char.                                                                                      |   |

|                | and            | 01h                                   | ; Bit one contains SCC                                                                                          |   |

|                |                |                                       | ; received character flag                                                                                       |   |

|                | jr             | z,cont                                | , वर्त्त र                                                                                                      |   |

|                | in             | a,(a3h)                               | ; Input received char.                                                                                          |   |

|                | ld             | (temp),a                              | ; Save character                                                                                                |   |

|                |                | · · · · · · · · · · · · · · · · · · · |                                                                                                                 |   |

| Check          | for rec        | eive errors                           | 2                                                                                                               |   |

|                |                |                                       | · · · · · · · · · · · · · · · · · · ·                                                                           |   |

|                | ld             | a,01h                                 |                                                                                                                 |   |

|                | out            | (a1h),a                               | ; Point to error status reg.                                                                                    | ( |

|                | in             | a,(a1h)                               | , .                                                                                                             | K |

|                | and            | 70h                                   | ; Zero all non-error bits                                                                                       |   |

|                | call           | nz,err                                | ; Call error handling routine                                                                                   |   |

|                |                |                                       | ; for receive error                                                                                             |   |

|                | ld             | a,(temp)                              | ; Restore data                                                                                                  |   |

|                | call           | console                               | ; Output through console                                                                                        |   |

|                | }              | ·                                     |                                                                                                                 |   |

| Note:          |                |                                       | ar, and err subroutines are dependent on                                                                        |   |

|                | the sy         | vstem being u                         | isea.                                                                                                           |   |

| Tuona          | mit oh         | aracter                               |                                                                                                                 |   |

| 114115         |                | anacter                               |                                                                                                                 |   |

| cont:          | in             | a,(a1h)                               | ; Check for transmitter ready                                                                                   |   |

| cont.          | and            | 04h                                   | ; Xmit status is in bit 3                                                                                       |   |

|                |                | z,next                                |                                                                                                                 |   |

| Trane          | . jr<br>mitter | is ready                              |                                                                                                                 |   |

| 110119         | call           | getchar                               | ; Get next char. to be transmitted.                                                                             | ( |

|                | out            | (a3h),a                               | : Transmit data                                                                                                 |   |

|                | out            |                                       | ; Check for received char.                                                                                      |   |

|                | jr             | next                                  | $\cdot$ C DOCK THE FOCATVAN COST                                                                                |   |

Υ.

### 4-18

| ; SCC initializa   | ation table |                             |

|--------------------|-------------|-----------------------------|

| ;<br>sccinit: defb | 04h         | : Point to WR4              |

| defb               | 44h         | ; X16 clock                 |

| ucib               | -1 111      | ; No parity                 |

|                    |             | ; One stop bit              |

| defb               | 03h         | : Point to WR3              |

| defb               | 001h        | ; Receive 8 bits/character  |

| den                | ocm         |                             |

| 1.0                | 051         | ; Enable Receiver           |

|                    | 05h         | ; Point to WR5              |

| defb               | 0eah        | ; Transmit 8 bits/character |

|                    |             | ; Set RTS and DTR outputs   |

|                    |             | ; Enable receiver           |

| defb               | 0bh         | ; Point to WR11             |

| defb               | 5 <b>6h</b> | ; Receive $clock = BRG$     |

|                    |             | ; Transmit clock $=$ BRG    |

|                    |             | ; TRxC outputs BRG          |

| defb               | 0ch         | ; Point to WR12             |

| defb               | 06h         | ; Init. low byte of time    |

|                    |             | : constant for 9600 baud    |

| defb               | 0dh         | ; Point to WR13             |

| defb               | 00h         | ; Init. high byte of time   |

|                    |             | ; constant for 9600 baud    |

| defb               | 0eh         | ; Point to WR14             |

| defb               | 01h         | : Use 2.4576 MHz clock      |

| ucib               | V 4 11      | ; for baud rate generator   |

|                    |             | : source                    |

|                    |             | ,                           |

|                    |             | ; Enable BRG                |

### 4.6 REAL TIME CLOCK PROGRAMMING

The Real Time Clock uses 23 registers (counters or RAM) for programming. Reading or writing to any of these registers is done in two steps. First, the register address is written to port 5. Then an input or output operation to port 6 accesses the desired register. Table 4-7 lists the register functions and addresses.

### Table 4-7. RTC REGISTER FUNCTIONS AND ADDRESS CODES

### NOTE: All other addresses are unused

\*

| Function                   | RTC Register<br>Address | ( |

|----------------------------|-------------------------|---|

| Counter0001 of a second    | 00H                     |   |

| Counter01 & .1 of a second | 01H                     |   |

| Counter - second           | 02H                     |   |

| Counter - minute           | 03H                     |   |

| Counter - hour             | 04H                     |   |

| Counter - day of the week  | 05H                     |   |

| Counter - day of the month | 06H                     |   |

| Counter - month            | 07H                     |   |

| RAM0001 of a second        | 08H                     |   |

| RAM01 & .1 of a second     | 09H                     |   |

| RAM - second               | 0AH                     |   |

| RAM - minute               | 0BH                     |   |

| RAM - hour                 | 0CH                     |   |

| RAM - day of the week      | 0DH                     |   |

| RAM - day of the month     | 0EH                     | 1 |

| RAM - month                | 0FH                     | ( |

| Interrupt Status Register  | 10H                     |   |

| Interrupt Control Register | 11 <b>H</b>             |   |

| Counter Reset              | 12H                     |   |

| RAM Reset                  | 13H                     |   |

| Status Bit                 | 14H                     |   |

| GO Command                 | 15H                     |   |

| STANDBY INTERRUPT          | 16H                     |   |

| Test Mode                  | 1FH                     |   |

### 4.6.1 Real Time Counter

The real time counter consists of four-bit digits with two digits being used during any read or write cycle. The digits define a BCD number as shown in Table 4-8. During a read cycle, the unused bits remain at a logical zero and, during a write cycle, the unused bits are disregarded. An unused bit is defined as any bit that does not yield a full BCD number. As an example, there is a limit on the possible numbers for tens of hours. Tens of hours has an upper limit of two. Therefore, two bits are all that is necessary to define tens of hours. This leaves two bits unused. The unused bits appear in Table 4-8 as dashes.

4-20

| ( | = | U | n | us | ed | . 1 | oit | ts) | ) |

|---|---|---|---|----|----|-----|-----|-----|---|

|---|---|---|---|----|----|-----|-----|-----|---|

| ) | Counter Addressed                                                                                  | Units<br>D0 D1 D2 D3                                                                               | Max Tens<br>BCD D4 D5 D6 D7<br>Code      | Max<br>BCD<br>Code         |

|---|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|

|   | 1/10000 sec<br>1/100 & 1/10 sec<br>second<br>minute<br>hour<br>day of the week<br>day of the month | D0 D1 D2 D3<br>D0 D1 D2<br>D0 D1 D2 D3 | 9 D4 D5 D6<br>9 D4 D5 D6<br>9 D4 D5<br>7 | 9<br>9<br>5<br>2<br>0<br>3 |

|   | month                                                                                              | D0 D1 D2 D3                                                                                        | 9 D4                                     | 1                          |

### 4.6.2 RAM

There are 56 bits of RAM located on the chip. The bits provide a means for storage whenever there is a power down. They also serve as an alarm latch for comparison with the real time counter. This comparison is performed on all digits except the ten thousandths of a second and the tens of days of the week. These digits are not used by the real time counter. When the two most significant bits of any RAM digit are ones, the RAM location will always match the real time counter.

The RAM has the same format as the real time counter. There are four bits per digit and a total of 14 digits. Every bit is used. The unused bits in the real time counter are compared to zeros in the RAM.

### 4.6.3 Interrupts

The MM58167A Microprocessor has two interrupt outputs. The INTERRUPT OUTPUT yields a true high signal. There are eight possible programmable interrupt rates: 10 per second, one per second, one per minute, one per hour, one per day, one per week, one per month, and during a RAM/real time counter comparison. The output is enabled when a one is written in the interrupt control register. The bit location is related to the desired output frequency. When one or more bits are set in the interrupt control register, the counter's rollover will clock the interrupt status register and the interrupt output will go high. Read the interrupt status register to identify which frequency created the interrupt and to reset the interrupt. A one will appear in the bit position as an identifier for the interrupting frequency. The format of the interrupt status register and interrupt control register is given in Table 4-9. The interrupting frequency is identified by a one in the respective bit position.

# Table 4-9. INTERRUPT CONTROL AND INTERRUPT STATUS REGISTER FORMAT

Bit **Interrupt Rates** D0 Counter/RAM comparison D1 10 per second D2 one per second D3 one per minute D4 one per hour D5 one per day D6 one per week D7one per month

The STANDBY INTERRUPT occurs when enabled and during a RAM/real time counter comparison. This interrupt mode is intended to be used when the host system is powered down. Additional circuitry would be needed for the host to recognize this signal and turn the power on to service the interrupt. The STANDBY INTER-RUPT is enabled by writing a one into RTC register 16H and is disabled by writing a zero. The interrupt is triggered by the level of the compare signal. If the compare is enabled when the STANDBY INTERRUPT is first enabled the interrupt will turn on immediately.

#### 4.6.4 Counter and RAM Resets

The set of digits (counter or RAM) to be reset is determined by the data that is written into the RTC reset registers. Table 4-10 shows the data format needed to reset desired counters or RAM. Writing to RTC register 12H resets counters and writing to RTC register 13H resets RAM. A logical one on the data bus will cause two digits to be reset. Resetting the most significant used bit of any counter will increment the following counter.

# Table 4-10. RTC COUNTER AND RAM RESET FORMAT

NOTE: For counters, reset address = 12HFor RAM, reset address = 13H

| )            | Counter or RAM                                                                                                                                                                                                                                                                                                                                      | Reset              | D0                                   | D1                                   | D2                                   | D3                              | D4                              | D5                              | D6                                   | D7                                        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------------|---------------------------------|---------------------------------|--------------------------------------|-------------------------------------------|

|              | 1/10000 sec<br>1/100 & 1/10 sec<br>second<br>minute<br>hour<br>day of the week<br>day of the month<br>month<br>4.6.5 RTC Prog                                                                                                                                                                                                                       |                    | 1<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>1<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1 |

| $\Big)$      | <ul> <li>REAL TIME CLOCK PROGRAMMING EXAMPLE</li> <li>FOR INSTRUCTIONAL PURPOSES ONLY</li> <li>All port addresses are for the standard factory settings.</li> <li>a5h = real time clock address select register</li> <li>a6h = real time clock access (using the register address in po a5h)</li> <li>Reset all real time clock counters</li> </ul> |                    |                                      |                                      |                                      |                                 | ı port                          |                                 |                                      |                                           |

|              | out (<br>ld a                                                                                                                                                                                                                                                                                                                                       | (a5h),a            |                                      |                                      | cour<br>l cou                        |                                 |                                 | regi                            | ster                                 |                                           |

| $\mathbf{)}$ | out (<br>ld a                                                                                                                                                                                                                                                                                                                                       | a,13h ;<br>(a5h),a | Poir                                 | nt to                                | s<br>RAN<br>RA                       |                                 |                                 |                                 | er                                   |                                           |

4-23

. ş. ζ. Set RTC minutes counter to six ÷., ld a,03h ; Point to RTC minutes counter (a5h),a out ld a,06h ; Set minutes to six (a6h),a out Set RTC hours counter to eight ld a,04h ; Point to RTC hours counter out (a5h).a ld a.08h (a6h),a ; Set hours to eight out Give RTC the 'GO' command 1.4 This command resets the seconds, tenths and milliseconds counters. The name 'GO' is misleading since the clock is never stopped. ; Point to 'GO' register ld a.15h out (a5h).a : Give 'GO' command ld a.0h out (a6h),a Set interrupt rates for one per minute : Point to interrupt control ld a,11h ; register out (a5h),a ld a.08h (a6h).a ; Set interrupts out : Initialize processor's interrupts di ; Set Z80 interrupt mode one im 1 ld a,0c3h ld (38h),a : Init interrupt vectors ld hl.rdclk ld a.1 ld (39h).a ld a,h 1 × 30 ld (3ah),a 100. ei 1. halt cont: ; Wait for interrupts jr cont

4-24

| rdclk:  | ld      | a,03h           |                             |

|---------|---------|-----------------|-----------------------------|

|         | out     | (a5h), <b>a</b> | ; Point to minutes counter  |

|         | in      | (a6h),a         | ; Read minutes counter an   |

|         | ld      | (min),a         | ; store at min.             |

| Read R  | TC ho   | ours counter    |                             |

|         |         | _               |                             |

|         | ld      | a,04h           | ; Point to hours counter    |

|         | out     | · · · ·         |                             |

|         | in      | (a6h),a         | ; Read hours counter and    |

|         | ld      | (hour),a        | ; store at hour             |

| Reset r | eal tir | ne clock inte   | rrupts                      |

|         |         |                 | •                           |

|         | ld      | a,10h           | ; Point to interrupt status |

|         | out     | (a5h), <b>a</b> | ; register                  |

|         | in      | (a6h), <b>a</b> | ; Input from register reset |

|         |         |                 | ; interrupt                 |

|         | reti    |                 | ; Return for next interrup  |

###

#

in a statistical statisticae statisticae statisticae -

•

and the second  $(*) = j_{1} + j_{2} + j_{3} + j_{4}$ A.3. 1  $\gamma_{i_{1}}$   $\gamma_{i_{2}}$   $\gamma_{i_{2}}$   $\gamma_{i_{2}}$   $\gamma_{i_{2}}$

and the second second

# SECTION V ENVIRONMENTAL CONSIDERATIONS

5.0 GENERAL

The I/O-8 is contained on a printed circuit board of the size and characteristics defined by the IEEE-696 specification.

The I/O-8 regulates the voltages supplied by the IEEE-696 bus down to those DC voltages required by the on-board circuitry.

5.1 ELECTRICAL REQUIREMENTS AND SPECIFICATIONS

5.1.1 +5 Volt Regulation

The I/O-8 regulates the +8 volts (unregulated) input down to +5 volts with a maximum or  $\pm .25$  volts of ripple.

5.1.2 +12 Volt Regulation

The I/O-8 regulates the  $\pm 16$  volts (unregulated) input down to  $\pm 12$  volts with a maximum of  $\pm .5$  volts of ripple.

5.1.3 Current Consumption (Estimated)

| $\pm 12$ VDC | 150 milliamperes (maximum)<br>114 milliamperes (typical) |

|--------------|----------------------------------------------------------|

| -12 VDC      | 138 milliamperes (maximum)<br>108 milliamperes (typical) |

| +5 VDC       | 1.78 amps (maximum)                                      |

1.19 amps (typical)

5.1.4 Power Consumption (Estimated)

19.94 watts (maximum) 13.68 watts (typical)

### 5.2 PHYSICAL SPECIFICATIONS

5.2.1 Dimensions

The I/O-8 printed circuit board dimensions are 5.125 x 10.0 inches.

5-1/5-2

# APPENDIX A SELECTED IEEE-696 SPECIFICATION SHEETS

NOTE: For additional information, see the complete document "IEEE Standard 696 Interface Devices."

# IEEE-696 bus pin list

| Pin<br>No. | Signal &<br>Type | Active<br>Level                       | Description                                                                                                                     |

|------------|------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1 +8 V(B)  |                  | · · · · · · · · · · · · · · · · · · · | Instantaneous minimum greater<br>than 7 V, instantaneous maxi-<br>mum less than 25 V, average<br>maximum less than 11 V.        |

| 2          | +16 V(B)         |                                       | Instantáneous minimum greater<br>than 14.5 V, instantaneous maxi-<br>mum less than 35 V, average<br>maximum less than 21.5 V.   |